PC Gamer 报导,台积电宣布启动下代系统级晶圆(System-on-Wafer,SoW)封装开发,命名为「SoW-X」。将使市场中央处理器(CPU)和图形处理器(GPU)晶片面积显得微不足道,为追求极致运算能力的资料中心和人工智慧(AI)领域带来颠覆性的变革。

智慧手机、穿戴式装置、行动游戏机,到桌上型电脑、伺服器,以及大型资料中心设备都能看到处理器的身影的情况下,使得晶片的尺寸各异。而当前高阶个人电脑中的处理器,无论是 AMD 的 Ryzen 9 9950X3D 或英特尔 Core Ultra 9 285K 处理器,都採多个小型晶片(chiplets),就是将多个晶片整合封装成一个大型处理器的技术。而台积电的 SoW-X 技术,正是这种晶片整合概念的更进阶实现。

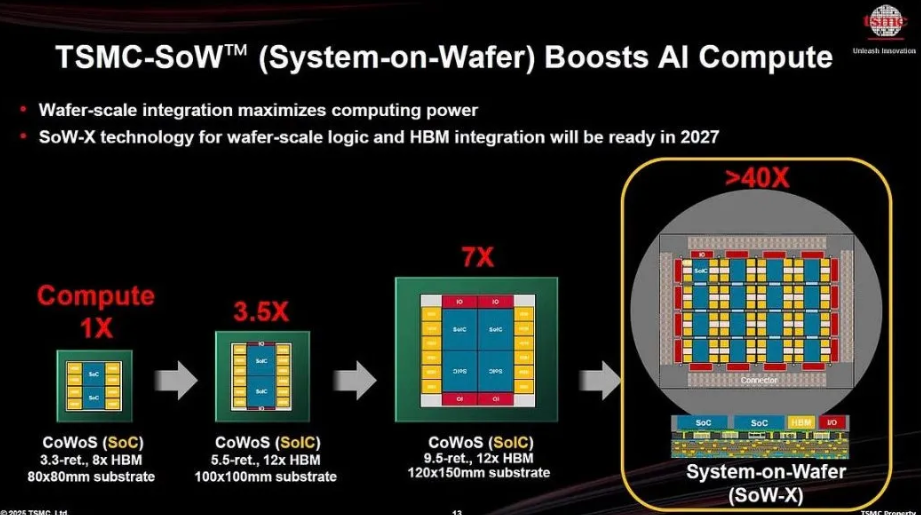

与现有技术相比,SoW-X 展现出惊人的规模和整合度。传统的晶片封装技术士通常在约 7,000mm² 的基板上安装三到四个小型晶粒。然而,SoW-X 晶片封装技术的覆盖面积将提升 10~15 倍,甚至需要使用整片 12 吋晶圆。最引人注目进步之一,在于同片晶圆整合更多关键元件。台积电第一代 SoW 封装仅将处理晶粒安装到晶圆,新版 SoW-X 能直接含高频宽记忆体(HBM)晶片。这项突破性的整合技术代表着无需再仰赖昂贵,且複杂的外部互连(interconnects)来连接记忆体和处理器,极大的简化了系统设计并提升了效率。

为了具体展现 SoW-X 的庞大规模,即使是目前 AMD 用于 AI 应用的大型 MI300X 处理器,在 SoW-X 面前也显得异常微小。事实上,AMD 的 MI300X 本身已是一个工程奇蹟,因为其中包含 20 个晶片和晶粒,其中包括四个大型 I/O 基础晶粒、八个 CNDA 3 GPU 和八个 HBM 模组,而台积电的 SoW-X 有可能将其规模再乘以十倍。

这种庞大的 SoW-X 产品并非能轻易安装到现有的介面插槽中。由于所有晶粒都安装在同一片晶圆上,该晶圆必须额外叠加多层结构,以有效散热、提供电力,并在系统内部传输数据。因此,虽然晶圆本身是纤薄、精密的物件,但一旦经过 SoW-X 封装,它们就会变成庞大、沉重且巨大的设备。因此,SoW-X 的主要应用场景将锁定在超大型 AI 资料中心中,在这些对运算密度有着极高要求的环境中,如何在最小的空间内塞入最多的处理能力,是最大化资料中心设备内部可用空间关键。如此,SoW-X 不仅是为了製造更大、更好的处理器,它更是将摩尔定律 (Moore’s Law) 的极限推向新的高峰。

除了追求绝对的运算性能,SoW-X 在能源效率方面也带来显着的改善。藉由尽可能将多的元件放置在同一个基板上,可以大幅降低功耗。儘管台积电指出 SoW-X 的总功耗将高达 17,000 瓦,但其相对效能功耗比(performance-per-watt) 却比传统透过 PCIe 介面连接所有组件的资料中心丛集高出 65%,这代表着在提供相同,甚至更高运算能力的同时,SoW-X 能够更有效地利用能源。

对广大游戏玩家和普通家庭用户而言,SoW-X 目前可能看似遥远。然而,台积电透过 SoW-X 系统开发和出货所积累的知识与经验,将会逐渐下放到其日常的封装产品中。这代表着未来的手机、桌面 CPU 和显示卡都将受惠于此,无论它们目前是否已採用晶粒,或晶片堆叠技术,还是在节点製程达到单一晶粒电晶体数量的实际限制时。

台积电预估 SoW-X 2027 年才会问世。届时非常高昂的製造成本,只有少数特定的客户负担得起。这项技术的问世,也引发了业界对未来晶片发展方向的思考,那就是 SoW-X 之后,晶圆是否需要变得更大?或者我们将看到系统级晶圆叠晶圆(system-on-wafer-on-wafer)的发展,以继续推动对更强大处理能力的追求。

儘管电晶体尺寸可能无法再大幅缩小,但可以肯定的是,未来的处理器将会变得巨大得多。台积电持续在晶片技术的突破,最终将会是不需要挑选合作伙伴,只需耐心等待,因为最终所有客户都会找上门来。这也将使得在台积电预计 2025 年获利将突破 500 亿美元的背景下,SoW-X 无疑再次巩固全球半导体製造领导地位。

微信扫一扫打赏

微信扫一扫打赏

支付宝扫一扫打赏

支付宝扫一扫打赏